2019-04-12 21:06 — asano

カテゴリー:

50ピンのコネクタに刺さっていたジャンパーピンはREADYをGNDに落とすためのもの、34ピンコネクタに接続していないからです。いずれDSKCHGと切り替えられるようにしたいですね。

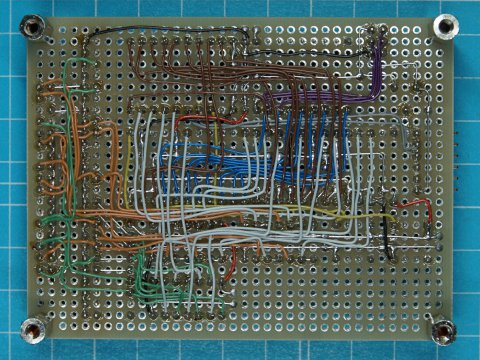

裏側、FDDコネクタのところ以外はほとんど一対一の接続なので配線作業は楽でした。

ATmega1284Pのポート割り当ては以下のようになっています。

| Port | I/O | 接続先 | 備考 |

|---|---|---|---|

| PA0 | 未使用 | ||

| PA1 | 未使用 | ||

| PA2 | 未使用 | ||

| PA3 | 未使用 | ||

| PA4 | 未使用 | ||

| PA5 | 未使用 | ||

| PA6 | 未使用 | ||

| PA7 | 未使用 | ||

| PB0 | I/O | HD63265PのD0 | 通常は入力モード、レジスタ書き込み時のみ出力に切り替え |

| PB1 | I/O | HD63265PのD1 | |

| PB2 | I/O | HD63265PのD2 | |

| PB3 | I/O | HD63265PのD3 | |

| PB4 | I/O | HD63265PのD4 | |

| PB5 | I/O | HD63265PのD5 | |

| PB6 | I/O | HD63265PのD6 | |

| PB7 | I/O | HD63265PのD7 | |

| PC0 | O | HD63265PのRS | |

| PC1 | O | HD63265PのRD | |

| PC2 | O | HD63265PのWR | |

| PC3 | O | HD63265PのCS | |

| PC4 | O | HD63265PのDACK | |

| PC5 | I | HD63265PのDREQ | |

| PC6 | I | HD63265PのINT | |

| PC7 | O | HD63265PのRESET | |

| PD0 | I | TTL-232R-5VのTXD | |

| PD1 | O | TTL-232R-5VのRXD | |

| PD2 | I | DSKCHG | |

| PD3 | O | IN USE | |

| PD4 | O | MOTOR | |

| PD5 | O | DENSEL | |

| PD6 | I | INDEX | FDDの回転数を測れるように |

| PD7 | O | HD63265Pの8/5 |

アナログ入力としても使えるPA0~PA7は予備であけてあります。また、DMAモード・Non-DMAモードともに使えるようにしていますが、最終的にはどちらか一方にする予定です。

FDDのドライブセレクト信号について。

HD63265PからはUS0, US1よりバイナリで出力されているのでデコーダが必要なのですが、複数のドライブを同時には接続しないと割り切って前記の信号をそのままSN7438Nに入力しています。そのためソフトウェアからはドライブは3を指定する必要があります。

一方SN7438Nの出力はDS1へ接続しているので、ドライブのジャンパはDS1(0,1,2,3の1)を選んでおきます。

ドライブへの接続はリボンケーブルですが、5.25インチドライブのカードエッジソケットは入手が難しいです。昔のPCマザーボード付属のケーブルを流用しました。新しいものでは3.5インチ用が1つのものが多いですが、古いものでは3.5インチ用と5.25インチ用が2つずつ付いているものがありました。捻ってあるAドライブ用の部分を切断してストレートなBドライブ用のところを利用します。

参考文献・関連図書:

HD63265ユーザーズマニュアル, Hitachi.

ATmega164A/164PA/324A/324PA/644A/644PA/1284/1284Pデータシート, Atmel.

コメントを追加