PLLシンセサイザ(その14)

カテゴリー:

今回はその9で軽く触れたリングオシレータの電源を電流制御にするのを試したいと思っていたのですが、いろいろあって全く進捗していないので......

初期に作った74LS624にるVCOと74HC4046によるVCOのF-V特性を測ってみました。

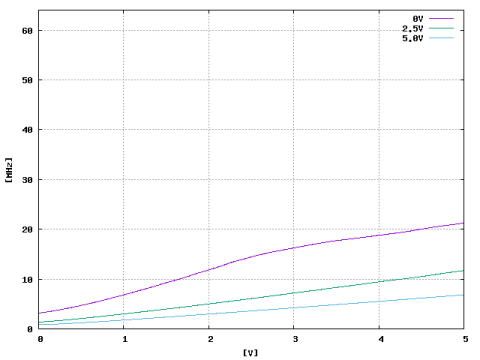

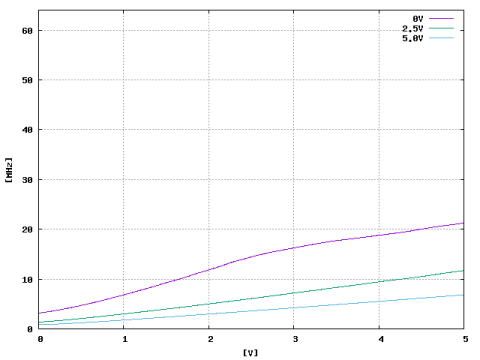

まずは74LS624です。

Cx=47pF でRNGを 0V, 2.5V, 5V と変化させた場合です。

リングオシレータを見た後では可変範囲狭いなという印象が強いですね。

今回はその9で軽く触れたリングオシレータの電源を電流制御にするのを試したいと思っていたのですが、いろいろあって全く進捗していないので......

初期に作った74LS624にるVCOと74HC4046によるVCOのF-V特性を測ってみました。

まずは74LS624です。

Cx=47pF でRNGを 0V, 2.5V, 5V と変化させた場合です。

リングオシレータを見た後では可変範囲狭いなという印象が強いですね。

前回周波数カウンタ機能が動き始めたので今回はいよいよVCOのF-V特性の自動測定です。

D/A値を0~4095まで5刻みで増加させながら以下を実行していきます。

ターミナルソフトでこれを記録しておきグラフなどの処理を行ないます。

2.で待つのは2つの理由があります。

一つはVCOの応答を待つため、とは言ってもループフィルタなどは通っていないので遅延は大きくないはずです。

もう一つは...... こちらの方が重要です。前回書いたようにゲート時間は256msあり、しかもタイマ割り込みで非同期に動いています。仮にゲート時間が始まった直後にD/Aを変更したとするとその結果が出るのは256ms後になります。しかもゲート時間が始まってからVCOの周波数が変わるまでは不正な値をカウントしてしまいます。本来ゲートの切り替わりを2回待つべきですが、0.5秒以上待つことで済ませてしまいました。

今回は...... PLLシンセサイザ関係ではあるのですが、ちょっと脱線してみます。

実験用に作った基板にはPLL ICの初期化用にAVRマイコンを搭載しており、VCOの実験用にD/Aコンバータも搭載しています。マイコンにはカウンタ・タイマも載っているのでちょっとソフトウェアを追加すれば周波数カウンタ機能も実現できそうです。

外部に周波数カウンタを接続すればいいではないかと思われるかもしれませんが、D/Aコンバータの出力を変化させながら周波数を測定できればVCOのF-V特性を自動的に測定できる可能性があります。

ということでまずは可能性を探っていきます。

周波数は簡単には1秒間のパルス数を数えれば良いわけですが、カウンタの桁数が多く必要になる上に測定時間も長くなるので、16ms間のパルスを数えて16で割ることでkHz単位の値を得ることにします。

もう「その10」と2桁に達してしまいましたが、当面は何か進捗があるたびに書いていこうと思います。

今回は何が進捗したかというと、出力周波数を下げていくとロックしたりしなかったり不安定になる問題です。

1MHzというのはVCOを単独で動かして求めた可変範囲をもとに出せるはずと思っていたわけですが、ループフィルタの出力の範囲が狭い、あるいはその付近でVCOのF-V特性が急峻になっていて周波数が安定しない、という可能性もあります。

前回リングオシレータの電源云々と書いたのは後者の対策だったのですが、ちょっと実験するだけならもっと簡単な方法がありました。

それはリングオシレータを1段から5段に変更してみることです。これで同じ入力電圧に対する周波数は約1/5(容量などの影響でもうちょっと下がるはず)になります。

試してみると設定下限の300kHzまで安定に動作します。代わりに上限も下がって14MHz程度までしか出せなくなりました。

PLLシンセサイザの続きです。

間があいてしまったので今困っていることをまとめてみます。

1.と2.はループフィルタ問題だと思われるので本を読み漁っているのですが......

学生時代は制御研究室にいたこともあってフィードバック制御は馴染みではあるのですが、PLL回路には位相比較器とかVCOなどの見慣れないものが含まれています。本を頼りに求めてみたのですがどうも桁が違っているようで、何かを勘違いしているのかもしれません。

じっくり本は読み直すことにして、勝手のわかるフィルタ部分だけ先に求めてみます。

実験に使っているのは以下のラグ・リード・フィルタです。

前回は74LS624によるVCOを作成しましたが、当初の計画である1MHz~25MHzには上限が足りない上にV2のコントロールが必要です。

そこで74HC4046によるVCOも作ってみました。

これも部品点数の少ないシンプルなものですね。74HC4046も前に動かしているので基本それを踏襲していますが、R1を切り替え式から挿し替え式に変更しました。さらにR2も必要に応じて挿せるようにソケットを用意しました。

とりあえずR1=47kΩ, R2=∞(Open)としています。

これで前回同様に周波数の可変範囲を調べてみると、0.94MHz~23MHzとわずかに広くなったうえにV2のような別途コントロールしなくてはならないものもありません。