2019-01-29 21:35 — asano

カテゴリー:

新しいデバイスを手に入れても実際に動かすのは遅くなることが多いのですが、今回はすぐに動かせました。これも Twitter にさらしたおかげかもしれません。

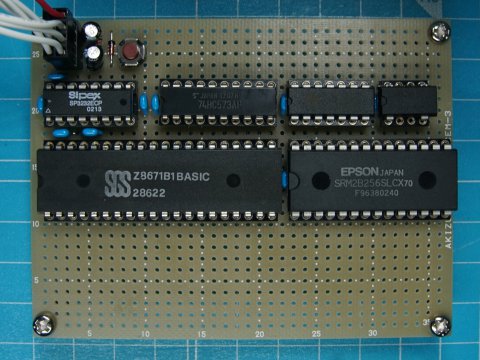

いつものように動作確認できる最小構成です。Zilogの資料では7チップとなっていますが、ROMを省略して(-1)、シリアルのレベルシフタを1488+1489⇒SP3232にして(-1)、クロックを独立発振器に変更して(+1)、なので合計6チップ構成です。

基板レイアウトはINS8073ボードやP8052AH-BASICボードとあわせています。電源・シリアルのコネクタも一緒です。

メインはもちろんZ8671B1です。実はROMを省略したことでちょっと問題があります。Z8671はリセット後に0FFFDH番地を読んでその下3ビットでシリアルのボーレートを決定します。そこでD0~D2をプルアップ/プルダウンして9600bpsを選択するようにしています。

右はおなじみのSRM2B256SLCX70、32k×8bitのSRAMです。0000H~7FFFHに配置していますが、0000H~07FFHまでは内蔵ROMと重なるので使用できません。

上の段に行って左端はSP3232ECP、シリアルのレベルシフタです。こんなのを積むより5VのままUSB変換ケーブルを繋いだほうが簡単ですが、INS8073, P8052AH-BASICのボードにあわせました。

右隣はTC74HC573AP、アドレスラッチです。これの位置はZ8671と接続しやすいように決めています。

その右は写真では読めませんがSN74HC00Nです。アドレスラッチのラッチパルスの反転とOEを作ります。Z8のバスってR/WとDSなのでちょっと面倒ですね。HM6117なら直結できそうです。

右端はSG-8002DC、7.3728MHzに設定しています。さっそくSG Writer IIが活躍しました。欲しい周波数が机の上で手に入るのは便利ですねぇ。

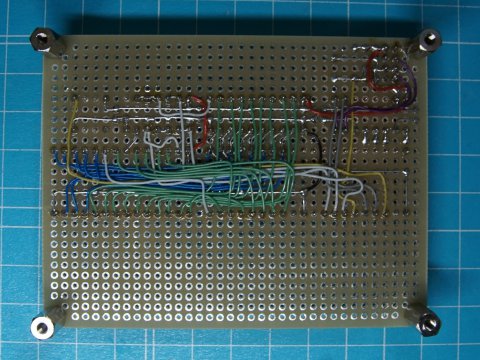

裏面の配線はいつものようにラッピング用単線をハンダ付けしています。

Z8671のポートはまだ空いているのでちょっとしたものならそのまま接続できますね。不足ならZ8671の下に40ピンDIPを乗せられるスペースがあります。

同様にSRAMの下にも28ピンDIPのスペースがあり、32k×8bitのROM/RAMが増設できます。ちょうど74HC00のゲートも1つ余っているのでA15を反転すれば良さそうに見えますが、ちょっと面倒なことがあります。

それは前述のROM省略の件です。8000H~0FFFFHまでにROMを配置するなら0FFFDHに当たるアドレスにボーレートを決める値を書いておけば済みます。

一方ROMを載せるということはそこからオートスタートさせる場合が多いでしょう。それには1020HからROMが配置されている必要があります。簡単なのは0000H~7FFFHにROMを8000H~0FFFFHにRAMを配置する方法ですが、これだとボーレートが不定になってしまいます。ゲートを追加するなどしてもう少し複雑なデコードする必要がありそうです。

コメントを追加